快訊

- 川習會MSCI季調登場 台股四萬二壓力測試、進入高檔整理

- 逾10萬公里折返跑 史國副總理杜札莉昨飛第四趟離台

- 為川習會暖身 美中財經首長週三將在南韓會晤

- 印尼在唐人街旁破獲史上最大非法網路賭博組織 逮捕逾300名外籍人士

- 北市知名產後護理之家疑涉裝偷拍設備 負責人喊冤:無功能廢線

- 快訊/伊朗已經向美國回答和談提議 以「停止戰爭」為核心

- 日經:日廠與台灣密切合作無人機 擺脫「紅色供應鏈」

- 伊朗沒在管停火 攻擊轟炸科威特、擊傷阿布達比出航的貨輪

- 中共民族團結進步促進法7月上路 羅文嘉分析:中華民族將等同中共專政

- 從美國副總統到國務卿都見了! 卡達超密集斡旋伊朗問題、天然氣輪首獲伊朗放行

- 「藍白做球讓習近平殺」!川習會前大砍軍購4700億 美國恐懷疑台灣防衛決心

- 藍黨團批選前承諾跳票:卓榮泰、賴清德勿成三班護病比絆腳石

- 有夠荒謬!俄閱兵日請烏軍停火 軍事專家揭烏方超猛無人機「飛1700公里直搗敵境」:不對稱戰力大發威

- 鄰近淺草寺!日本東京逾50年商店街確定拆除 7月底吹熄燈號

- 除毛診間被爆「裝監視器」客氣炸 聖宜診所3點聲明:提供現金退款

- 認罪繳1.2億元拚交保! 郭哲敏喊:柯文哲、陳歐珀都沒押 高院第5度打臉

- 日本琵琶湖一天發現三具浮屍! 有男有女警方調查中

- 波灣又有貨輪遇襲 伊朗放話:制裁國船隻別想通過荷姆茲海峽

- 漢他病毒郵輪靠岸!乘客今下船 多國派專機赴西班牙接人

- 許宇甄揭中央聯辦北棟管理費亂漲價:難怪百姓苦哈哈

【下一代CoWoS】台積電「化圓為方」投入CoPoS開發!CoWoP順勢崛起

2025-12-07 07:40 / 作者 戴嘉芬

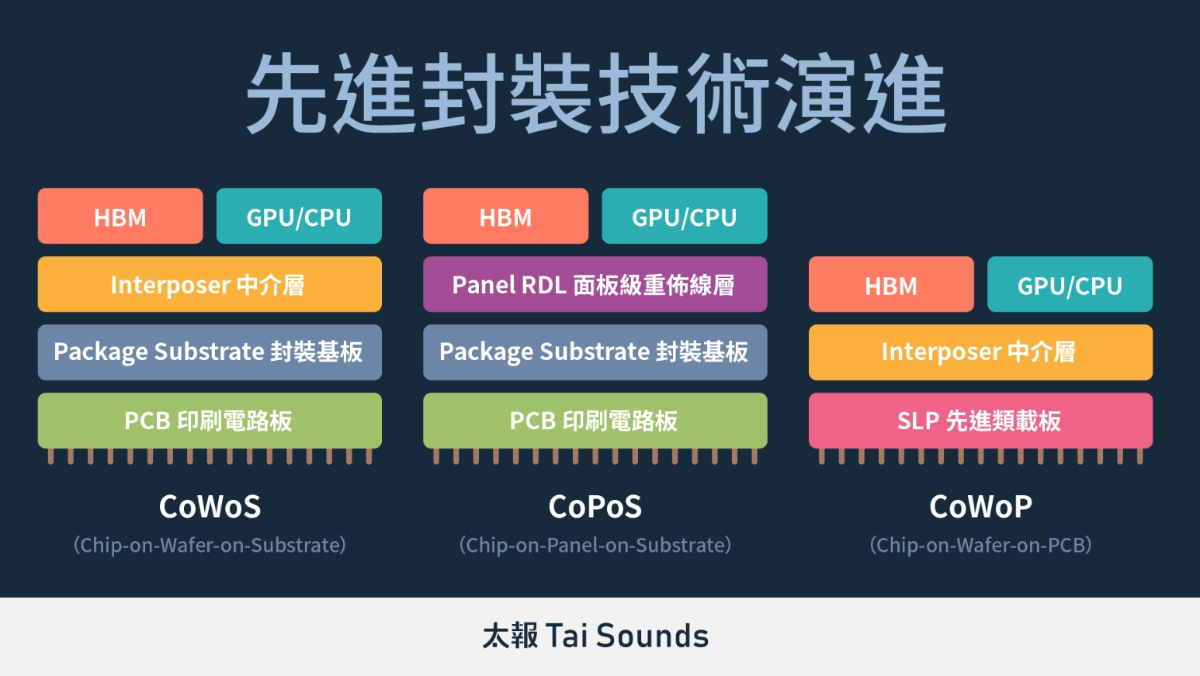

台積電積極擴充CoWoS產能,也致力開發下一代CoPoS封裝技術。此為先進封裝技術演進示意圖。太報繪製

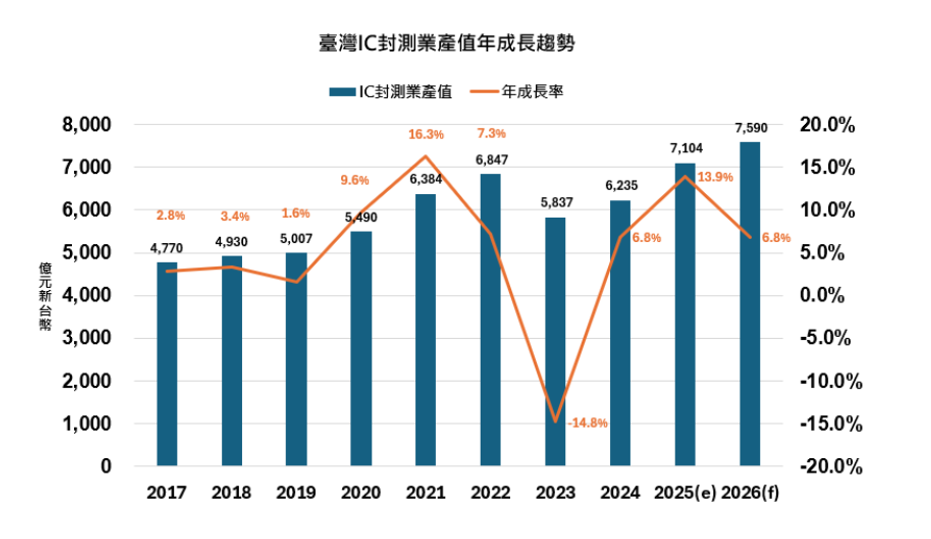

AI應用快速普及,高速運作晶片大量導入先進封裝,推升封測需求,台積電「CoWoS」成為家喻戶曉的先進封裝技術。除了CoWoS之外,台積電也積極開發下一代封裝技術如「CoPoS」,意即把CoWoS面板化,透過「化圓為方」來提升面積利用率與單位產量。還有一種「CoWoP」也被譽為次世代封裝技術,把晶片和中介層直接裝在高精度PCB板之上,有助於晶片散熱,但兩者在開發過程都面臨不同的挑戰,尚待克服。根據工研院產科國際所預估,2025年台灣半導體封測產業產值將達新台幣7,104億元,年成長率達13.9%。2026年,在AI/HPC基礎設施大規模部署需求下,封測產值將穩定成長至7,590億元,年增6.8%。

台灣半導體封測產值2026年將穩定成長至7,590億元,年增6.8%。工研院提供

工研院產科國際所分析師陳靖函表示,隨著摩爾定律逐漸逼近物理極限,單一晶片上的電晶體數量已難以持續呈指數成長,封裝技術遂成為決定晶片效能的關鍵。透過將多個小晶片緊密整合於單一IC中,可有效提升數據傳輸頻寬,並降低能耗與延遲,對追求極致記憶體頻寬與低延遲的AI晶片尤為關鍵。

為滿足這些需求,AI加速器普遍採用HBM(高頻寬記憶體),使得如 CoWoS(Chip-on-Wafer-on-Substrate)等可整合邏輯晶片與HBM的先進封裝技術,成為AI晶片供應鏈中的關鍵解方。

他進一步指出,半導體業界正持續研發透過異質整合將晶片互聯技術,結合先進、成熟製程節點,來設計、製造最新的SoC單晶片系統;再利用先進封裝技術,達到降低成本、縮短產品上市時間、提升系統效能的目的;而2.5D和3D封裝技術正是達成目標的關鍵。

工研院產科國際所分析師陳靖函認為,台灣在先進封裝領域的技術突破,也讓其成為全球半導體供應鏈的關鍵一環。戴嘉芬攝

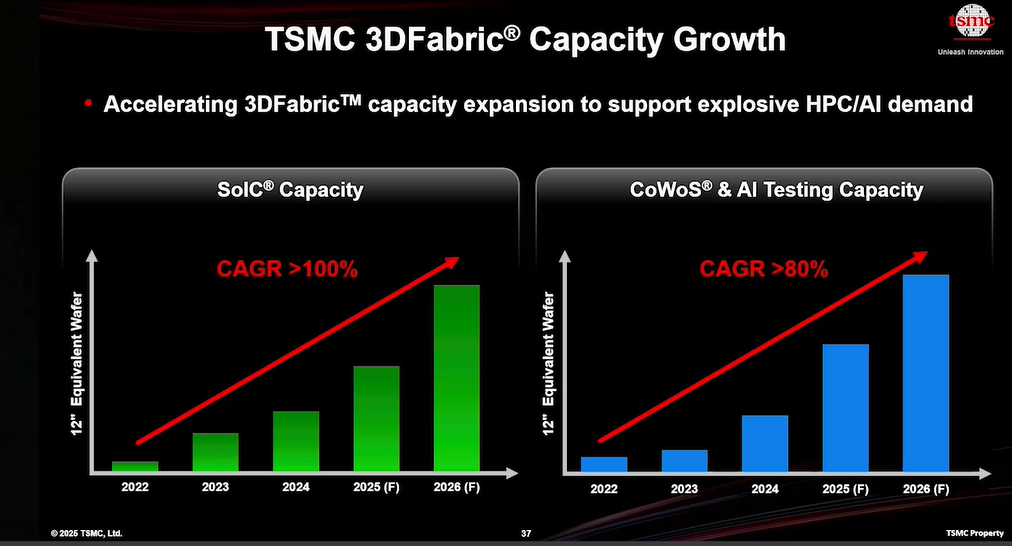

為了滿足客戶需求,台積電積極布局先進封裝,開發出 CoWoS、InFO 以及 SoIC 等技術,在竹科、中科、南科、嘉義都具備一定的產能。該公司指出,從2022年到2026年,SoIC 產能增長的年複合成長率(CAGR)將超過100%,CoWoS 產能增長的年複合成長率將超過80%。

台積電SoIC和CoWoS產能分別以100%、80%年複合成長率大量提升。取自TSMC

所謂 CoWoS(Chip-on-Wafer-on-Substrate),是把晶片堆疊起來,再封裝於基板上,以減少晶片空間。

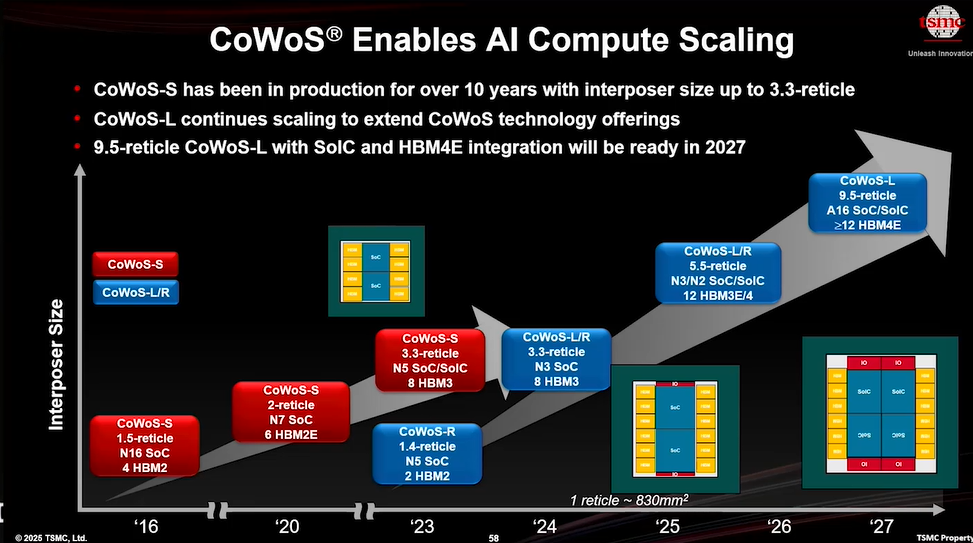

CoWoS 還細分為 CoWoS-S、CoWoS-R 和 CoWoS-R。台積電在10多年前就已開發出採用矽中介層封裝的 CoWoS-S技術,但因為造價昂貴,後來陸續開發出 RDL Interposer(重新分佈層)版本的 CoWoS-R;和 Si Bridge(矽橋)版本的 CoWoS-L,在必須銜接的高頻寬處做連結,目的是降低成本。

在AI應用興起後,台積電 CoWoS-L 需求大幅提升,銷量是 CoWoS 系列產品中最高的,約佔六成。與 CoWoS-S 相較,它的成本較為低廉,也能整合被動元件以及穩定電壓的元件,進而優化能源效率。

台積電預計在2026年推出5.5倍光罩尺寸的CoWoS-L技術;而9.5倍光罩尺寸的CoWoS則計劃於2027年量產。取自TSMC

CoWoS屬於2.5D封裝,而台積電3D封裝技術則包括SoIC-P和SoIC-X,前者採用微凸塊堆疊封裝;後者則採用Hybrid Bonding(混合鍵合)技術(註)。

根據美媒報導,台積電在美國興建的2座先進封裝廠,將專注於CoPoS和SoIC封裝技術,計畫在2026年啟動CoPoS測試生產工作,目標2027年底完成與合作夥伴之間的驗證工作。

台積電將在美國興建2座先進封裝廠。圖為亞利桑那晶圓1、2廠。取自TSMC

由於亞利桑那先進封裝廠尚未動土,目前CoWoS先進封裝採取與美商 Amkor(艾克爾)合作方式,來減緩產能不足的情形。Amkor在亞利桑那皮奧里亞市將建置1座價值20億美元的先進封測設施,預計2028年初投產。

在國內部分,據了解,台積電將透過子公司采鈺科技,於2026年設立首條CoPoS實驗線,預計2028年底至2029年上半年在嘉義AP7廠啟動量產。

IDC資深研究經理曾冠瑋近期受訪表示,預估兩年內,台積電先進封裝擴產重心還是以CoWoS為主,預計明年產能將成長60%,CoPoS將依計畫於2028年量產。估計在那一年,將有5%先進封裝產能從CoWoS移轉至CoPoS;其中,ASIC體系的自研晶片業者如Google、AWS較不需要大尺寸面板封裝,反而是GPU體系如輝達可能會採用CoPoS封裝。

IDC資深研究經理曾冠瑋認為,台積電CoPoS先進封裝在量產首年,估計將有5%比例從CoWoS移轉至CoPoS。戴嘉芬攝

除了台積電之外,日月光於全台北中南建置先進封裝產能,亦是全球最大的OSAT半導體封測廠。而國外廠商如英特爾則於美國、馬來西亞兩地建置封裝產能;三星布局更廣,包括韓國本地、中國和美國都有設廠。

陳靖函認為,對OSAT委外封測廠而言,在海外設廠將使營運成本增加,這是無可避免的。而封測廠的毛利可能不到晶圓廠(近60%)的一半,議價能力會因此受限,但如果不跟著去海外設廠,客戶可能會轉向當地供應鏈,甚至可能影響到整體供應鏈的穩定性。

在AI龐大需求下,先進封裝讓晶片量產時間逐漸縮短,從客戶設計定案(Tape-out)到量產,過去是7個季度,約一年半時間來開發一顆IC,如今搭配先進封裝技術,過程已縮短至3個季度,也就是不到一年就完成。

陳靖函指出,這樣的轉變對整個供應鏈造成極大壓力,IC製造業必須在產品製造時,一邊投入開發和驗證工作,也考驗供應鏈的彈性配合度。近年來,業界成立了3DIC先進封裝製造聯盟和矽光子產業聯盟,就是希望強化業界整合力道。

下一代封裝技術包括CoPoS、CoWoP(Chip-on-Wafer-on-PCB),旨在降低成本。在技術核心部分,相較CoWoS是先整合晶片與矽中介層,再安裝到ABF基板上。CoPoS(Chip-on-Panel-on-Substrate)則是把晶片排列在矩形基板上,最後再透過封裝製程連接到底層的載板上,讓多顆晶片可以封裝。

換句話說,CoPoS是將原本的圓形矽中介層,改用310×310mm矩形面板,也就是把CoWoS「面板化」,透過「化圓為方」來提升面積利用率與單位產量。至於CoWoP是今年新出現的先進封裝路線。則無須使用ABF基板,把晶片和中介層直接裝在高精度PCB板之上。

除了CoWoS之外,後面兩者皆在開發中。CoPoS主要挑戰來自於面板翹曲度的控制,且散熱效能受限於ABF基板,需額外加裝散熱解決方案。而CoWoP因採用精簡路徑和銜接大面積的PCB板,將有助於晶片散熱,但高精度PCB製造為其最大挑戰。

先進封裝技術演進示意圖。太報繪製

談到面板級封裝技術,力成資深副總林基正曾受訪指出,面板的優勢能提供大面積,尺寸大概是12吋晶圓的3倍多,利用率更可達4~6倍,相較圓形封裝技術,方形封裝在周圍四角較不會造成空間浪費,在成本、利用率和製造效率皆高出12吋晶圓,成本差距是雙位數百分比。

他也提到,力成研發面板級封裝已有6年,是國內開發面板級封裝最有經驗的業者。該公司FOPLP(扇出型面板級封裝)技術自2016年量產,最大尺寸為510x515mm,目前良率已接近90%,預估2028年達到放量,可望占力成營收比重約3成以上。

力成資深副總林基正指出,台積電也在開發面板級封裝技術,而力成開發出的面板封裝尺寸比台積電的更大。戴嘉芬攝

陳靖函指出,透過2.5D/3D IC堆疊技術,來自不同製程與供應商的邏輯晶片、記憶體與I/O控制器可整合於單一封裝中,提升系統效能並強化設計彈性。未來,這項高良率技術更有望延伸至CPO(共同封裝光學)等新一代封裝,進一步推動全球高速運算應用發展。

註:Hybrid Bonding(混合鍵合)是目前互連密度最高的技術。

最新more>

- 川習會MSCI季調登場 台股四萬二壓力測試、進入高檔整理

- 逾10萬公里折返跑 史國副總理杜札莉昨飛第四趟離台

- 為川習會暖身 美中財經首長週三將在南韓會晤

- 【懶人包】恐怖郵輪3死!漢他奪命時間軸曝光 罕見「人傳人」病毒致命達5成

- 「不存在適用所有人的理想揮棒」藍鳥打教鼓勵勇敢揮棒造就現在的岡本和真

- 誠品南西店傳「鼠出沒」 北市府晚間聯合稽查發現空汙防制設備有油煙逸散

- 普發現金2.0?羅明才提案:每人給1萬元「國民支援金」 草案進度曝光

- 印尼在唐人街旁破獲史上最大非法網路賭博組織 逮捕逾300名外籍人士

- 北市知名產後護理之家疑涉裝偷拍設備 負責人喊冤:無功能廢線

- 偷拍連環爆!達人教自保6大招 「靠手機就能查」免下載APP

熱門more>

- 愛爾麗→光澤診所!針孔偷拍「她」發現的 扮柯南「以圖搜圖」蒐證始末一次看

- 碩士生校門口創作意淫學生 台南女中火大提告

- 21歲啦啦隊美眉淪詐騙車手!「曾為12強應援」 收錢3次下場曝

- 快遞禮物竟變惡魔!FedEx司機綁架勒殺7歲女童 「她哭喊錄音曝光」家人心碎

- 台灣看過來!烏克蘭擁2利器源頭打擊 沒有愛國者飛彈也能制敵

- 塞揚獎、年度MVP很難全都要?大谷獨一無二身分恐掀口水戰

- 安檢太慢航班照飛!乘客氣得衝出「人肉擋機」 失控場面曝光

- YG混血練習生19歲離世!曾被看好進BABYMONSTER 韓網瘋傳死訊

- 悚!清大台積館女學生墜樓亡

- 一月賠掉一年!勞動基金單月虧損寫下歷史紀錄 新制勞退分紅縮水至2.2萬